Synthesis¶

Contents of this Page

Overview¶

The Python infrastructure shipped with the PoC-Library can launch manual, half-automated and fully automated synthesis runs. This can be done by invoking one of PoC’s frontend script:

poc.sh:

poc.sh <common options> <compiler> <module> <compiler options>

Use this fronend script on Darwin, Linux and Unix platforms.poc.ps1:

poc.ps1 <common options> <compiler> <module> <compiler options>

Use this frontend script Windows platforms.Attention

All Windows command line instructions are intended for Windows PowerShell, if not marked otherwise. So executing the following instructions in Windows Command Prompt (

cmd.exe) won’t function or result in errors!

See also

- PoC Configuration

- See the Configuration page on how to configure PoC and your installed synthesis tool chains. This is required to invoke the compilers.

- Supported Compiler

- See the Intruction page for a list of supported compilers.

See also

- List of Supported FPGA Devices

- See this list to find a supported and well known target device.

- List of Supported Development Boards

- See this list to find a supported and well known development board.

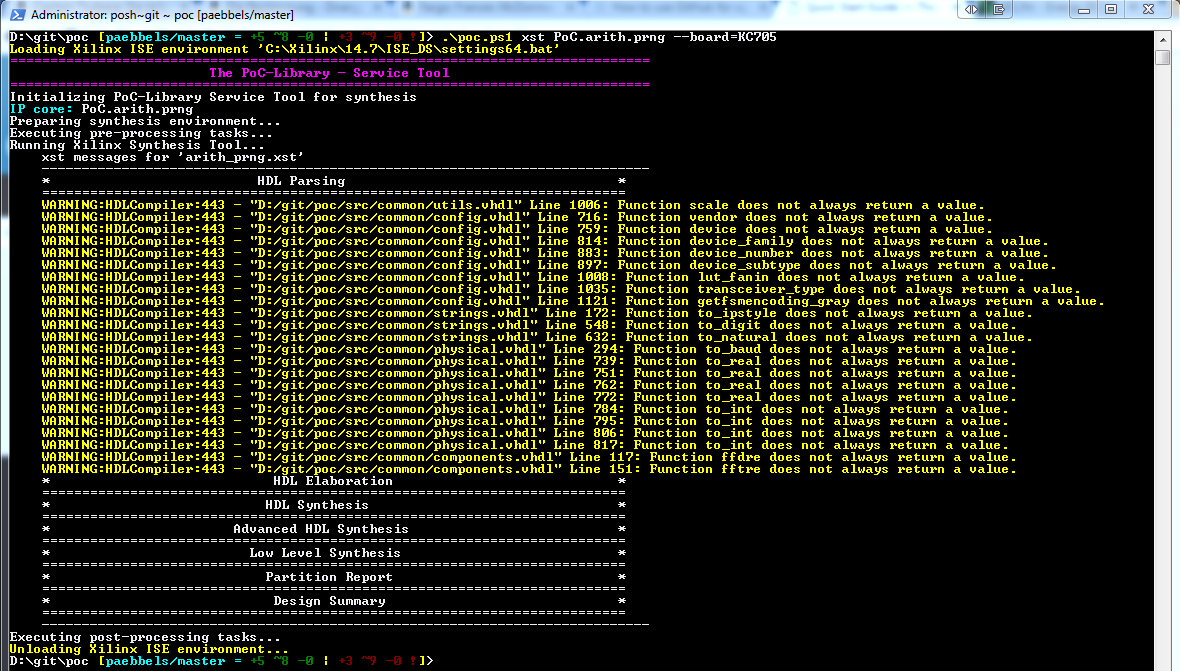

Quick Example¶

The following quick example uses the Xilinx Systesis Tool (XST) to synthesize a

netlist for IP core arith_prng (Pseudo Random Number Generator - PRNG). The

VHDL file arith_prng.vhdl is located at PoCRoot\src\arith and

virtually a member in the PoC.arith namespace. So the module can be identified

by an unique name: PoC.arith.prng, which is passed to the frontend script.

Example 1:

cd PoCRoot

.\poc.ps1 xst PoC.arith.prng --board=KC705

The CLI command xst chooses Xilinx Synthesis Tool as the synthesizer and

passes the fully qualified PoC entity name PoC.arith.prng as a parameter

to the tool. Additionally, the development board name is required to load the

correct my_config.vhdl file. All required source file are gathered and

synthesized to a netlist.

Running a single Synthesis¶

A synthesis run is supervised by PoC’s PoCRoot\py\PoC.py service tool, which offers a consistent interface to all synthesizers. Unfortunately, every platform has it’s specialties, so a wrapper script is needed as abstraction from the host’s operating system. Depending on the choosen tool chain, the wrapper script will source or invoke the vendor tool’s environment scripts to pre-load the needed environment variables, paths or license file settings.

The order of options to the frontend script is as following:

<common options> <synthesizer> <module> [<module>] <synthesizer options>

The frontend offers several common options:

| Common Option | Description | |

|---|---|---|

-q |

--quiet |

Quiet-mode (print nothing) |

-v |

--verbose |

Print more messages |

-d |

--debug |

Debug mode (print everything) |

--dryrun |

Run in dry-run mode | |

One of the following supported synthesizers can be choosen, if installed and configured in PoC:

Altera / Intel Quartus¶

The command to invoke a synthesis using Altera Quartus II or Intel Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option | Description | |

|---|---|---|

--board=<Board> |

Specify a target board. | |

--device=<Device> |

Specify a target device. | |

Example:

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

Lattice Diamond¶

The command to invoke a synthesis using Lattice Diamond is lse followed by a list of PoC entities. The following options are supported for the Lattice Synthesis Engine (LSE):

| Simulator Option | Description | |

|---|---|---|

--board=<Board> |

Specify a target board. | |

--device=<Device> |

Specify a target device. | |

Example:

cd PoCRoot

.\poc.ps1 lse PoC.arith.prng --board=ECP5Versa

Xilinx ISE Synthesis Tool (XST)¶

The command to invoke a synthesis using Xilinx ISE Synthesis is xst followed by a list of PoC entities. The following options are supported for the Xilinx Synthesis Tool (XST):

| Simulator Option | Description | |

|---|---|---|

--board=<Board> |

Specify a target board. | |

--device=<Device> |

Specify a target device. | |

Example:

cd PoCRoot

.\poc.ps1 xst PoC.arith.prng --board=KC705

Xilinx ISE Core Generator¶

The command to invoke an IP core generation using Xilinx Core Generator is coregen followed by a list of PoC entities. The following options are supported for Core Generator (CG):

| Simulator Option | Description | |

|---|---|---|

--board=<Board> |

Specify a target board. | |

--device=<Device> |

Specify a target device. | |

Example:

cd PoCRoot

.\poc.ps1 coregen PoC.xil.mig.Atlys_1x128 --board=Atlys

Xilinx Vivado Synthesis¶

The command to invoke a synthesis using Xilinx Vivado Synthesis is vivado followed by a list of PoC entities. The following options are supported for Vivado Synthesis (Synth):

| Simulator Option | Description | |

|---|---|---|

--board=<Board> |

Specify a target board. | |

--device=<Device> |

Specify a target device. | |

Example:

cd PoCRoot

.\poc.ps1 vivado PoC.arith.prng --board=KC705